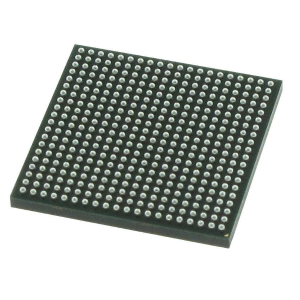

LCMXO1200C-3TN144I FPGA – Fjildprogrammearbere Gate Array 1200 LUT's 113 IO 1.8 /2.5/3.3V -3 Spd I

♠ Produktbeskriuwing

| Produktattribuut | Attribútwearde |

| Fabrikant: | Rooster |

| Produktkategory: | FPGA - Fjildprogrammearbere poarte-array |

| RoHS: | Details |

| Searje: | LCMXO1200C |

| Oantal logyske eleminten: | 1200 LE |

| Oantal I/O's: | 113 Yn/út |

| Oanfierspanning - Min: | 1.71 V |

| Oanfierspanning - Maks: | 3.465 V |

| Minimale wurktemperatuer: | - 40 graden Celsius |

| Maksimale wurktemperatuer: | + 100 °C |

| Datasnelheid: | - |

| Oantal transceivers: | - |

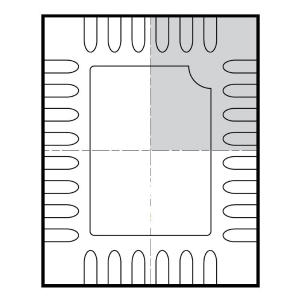

| Montagestyl: | SMD/SMT |

| Pakket/Koffer: | TQFP-144 |

| Ferpakking: | Bak |

| Merk: | Rooster |

| Ferdield RAM: | 6.4 kbit |

| Ynbêde blok RAM - EBR: | 9.2 kbit |

| Hichte: | 1,4 mm |

| Lingte: | 20 mm |

| Maksimale wurkfrekwinsje: | 500 MHz |

| Fochtgefoelich: | Ja |

| Oantal logyske arrayblokken - LAB's: | 150 LAB |

| Bedriuwsfoarsjenningsstroom: | 21 mA |

| Bedriuwsfoarsjenningsspanning: | 1,8 V/2,5 V/3,3 V |

| Produkttype: | FPGA - Fjildprogrammearbere poarte-array |

| Fabrykspakket kwantiteit: | 60 |

| Subkategory: | Programmeerbere logyske IC's |

| Totaal ûnthâld: | 15,6 kbit |

| Breedte: | 20 mm |

| Gewicht fan 'e ienheid: | 1,319 g |

Net-flechtich, ûneinich opnij konfigurearber

• Direkt oan – yn mikrosekonden oan

• Ien chip, gjin ekstern konfiguraasjegeheugen nedich

• Uitstekende ûntwerpfeiligens, gjin bitstream om te ûnderskeppen

• Konfigurearje SRAM-basearre logika yn millisekonden opnij

• SRAM en net-flechtich ûnthâld programmearber fia JTAG-poarte

• Stipet eftergrûnprogrammearring fan net-flechtich ûnthâld

Sliepmodus

• Maakt oant 100x statyske stroomreduksje mooglik

TransFR™ Rekonfiguraasje (TFR)

• Logika-update yn it fjild wylst it systeem wurket

Hege I/O nei logika-tichtens

• 256 oant 2280 LUT4's

• 73 oant 271 I/O's mei útwreide pakketopsjes

• Dichtheidsmigraasje stipe

• Leadfrije/RoHS-konforme ferpakking

Ynbêde en ferspraat ûnthâld

• Oant 27.6 Kbits sysMEM™ Ynbêde Blok RAM

• Oant 7.7 Kbits ferspraat RAM

• Spesjale FIFO-kontrôlelogika

Fleksibele I/O-buffer

• Programmeerbere sysIO™-buffer stipet in breed oanbod fan ynterfaces:

– LVCMOS 3.3/2.5/1.8/1.5/1.2

– LVTTL

– PCI

– LVDS, Bus-LVDS, LVPECL, RSDS

sysCLOCK™ PLL's

• Oant twa analoge PLL's per apparaat

• Klokfermannichfâldigjen, dielen en fazeferskowing

Stipe op systeemnivo

• IEEE Standert 1149.1 Grinsscan

• Ynboude oscillator

• Apparaten wurkje mei in stroomfoarsjenning fan 3.3V, 2.5V, 1.8V of 1.2V

• IEEE 1532-kompatibele yn-systeemprogrammearring